本文将会详尽解析PMOS、NMOS、CMOS、与门、或门、非门、与非门、或非门、同或门、异或门的原理。

并分享电源输入电路、PMOS和NMOS电路、与门电路、或门电路、非门电路、与非门电路、或非门电路、同或门电路、异或门电路的原理图、物料清单与PCB。文末还有点焊说明与上电调试的测试成果。

一、项目简介

「逻辑门」是数字电路上的基本单元,能够实现各类逻辑关系。「基本逻辑门分立元件电路」采用MOS管搭建而成,实现验证:与、或、非、与非、或非、同或、异或等逻辑运算。

二、原理解析

1.1 PMOS

PMOS是指N型衬底(SUB)、P沟道,靠空穴的流动运送电压的MOS管。

形成导通沟道须要负电荷吸引,低电平导通,高电平截至。

图1-1-1 PMOS符号与结构示意图

图1-1-2 PMOS开关控制电路图

使用PMOS控制时一般作为上管,放置在负载上方,常在PMOS上加一个上拉阻值,使PMOS载流子保持一个稳定的高电平初始状态,防止PMOS载流子电平遭到外界干扰形成不确定状态,保证PMOS默认在关掉状态。

当P0给低电平时,PMOS打开导通,LED亮起;

当P0给高电平常,PMOS关掉截至,LED熄灭。

1.2 NMOS

NMOS是指P型衬底(SUB)、N沟道,靠电子的流动运送电压的MOS管。

形成导通沟道须要正电荷吸引,高电平导通,低电平截至。

图1-2-1 NMOS符号与结构示意图

图1-2-2 NMOS开关控制电路图

使用NMOS控制时一般作为下管,放置在负载下方,常在NMOS上加一个下拉内阻,使NMOS载流子保持一个稳定的低电平初始状态,防止NMOS载流子电平遭到外界干扰形成不确定状态,保证NMOS默认在关掉状态。

当N0给低电平时,NMOS关掉截至,LED熄灭;

当N0给高电平常,NMOS打开导通,LED亮起。

1.3 CMOS

CMOS由PMOS与NMOS以对称互补的方式组成,C表示“互补”。静态帧率低,开关速度快,抗干扰能力强,工作效率高,集成度高,性能优越。

2.1 与门

与门(AND gate),又称逻辑积电路。

只有当输入都为高电平(逻辑1)时,输出才为高电平(逻辑1),否则输出为低电平(逻辑0)。

逻辑表达式:Y1=A1·B1

表1-1 与门真值表

图2-1-1 与门逻辑符号(矩形国标符号与形状特点符号)

图2-1-2 CMOS与门电路

图2-1-3 CMOS与门电路工作原理图图

如上图所示,CMOS与门电路的工作原理为:

① 当A1输入低电平,B1输入低电平时,Q1,Q2,Q5导通,Q3,Q4,Q6截至,Y1输出低电平;

② 当A1输入低电平,B1输入高电平常,Q2,Q5,Q6导通,Q1,Q3,Q4截至,Y1输出低电平;

③ 当A1输入高电平,B1输入低电平时,Q1,Q4,Q5导通,Q2,Q3,Q6截至,Y1输出低电平;

④ 当A1输入高电平,B1输入高电平常,Q3,Q4,Q6导通,Q1,Q2,Q5截至,Y1输出高电平;

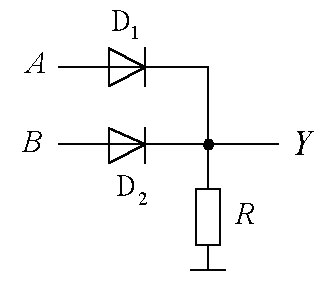

2.2 或门

或门(OR gate),又称逻辑和电路。

只要输入中有一个为高电平(逻辑1)时,输出就为高电平(逻辑1);只有当输入都为低电平(逻辑0)时,输出才为低电平(逻辑0)。

逻辑表达式:Y2=A2+B2

表1-2 或门真值表

图2-2-1 或门逻辑符号(矩形国标符号与形状特点符号)

图2-2-2 CMOS或门电路

图2-2-3 CMOS或门工作原理图

如上图所示,CMOS或门电路的工作原理为:

① 当A2输入低电平,B2输入低电平时,Q1,Q2,Q6导通,Q3,Q4,Q5截至,Y2输出低电平;

② 当A2输入低电平,B2输入高电平常,Q1,Q3,Q5导通,Q2,Q4,Q6截至,Y2输出高电平;

③ 当A2输入高电平,B2输入低电平时,Q2,Q3,Q4导通,Q1,Q5,Q6截至,Y2输出高电平;

④ 当A2输入高电平,B2输入高电平常,Q3,Q4,Q5导通,Q1,Q2,Q6截至,Y2输出高电平;

2.3 非门

非门(NOT gate),又称逻辑否电路。

当输入为低电平(逻辑0)时,输出为高电平(逻辑1);当输入为高电平(逻辑1)时,输出为低电平(逻辑0)。

逻辑表达式:Y3=A3’

表1-3 非门真值表

图2-3-1 非门逻辑符号(矩形国标符号与形状特点符号)

图2-3-2 CMOS非门电路

图2-3-3 CMOS非门电路工作原理图

如上图所示,CMOS非门电路的工作原理为:

① 当A3输入低电平时,Q1导通,Q2截至数字逻辑电路与系统设计第二版答案,Y3输出高电平;

② 当A3输入高电平常,Q2导通,Q1截至,Y3输出低电平;

2.4 与非门

与非门(NAND gate)是与门和非门的叠加结合。

只有当输入都为高电平(逻辑1)时,输出为低电平(逻辑0),否则输出为高电平(逻辑1)。

逻辑表达式:Y4=(A4·B4)’

表1-4 与非门真值表

图2-4-1 与非门逻辑符号(矩形国标符号与形状特点符号)

图2-4-2 CMOS与非门

图2-4-3 CMOS与非门工作原理图

如上图所示,CMOS与非门电路的工作原理为:

① 当A4输入低电平,B4输入低电平时,Q1,Q2导通,Q3,Q4截至,Y4输出高电平;

② 当A4输入低电平,B4输入高电平常,Q2,Q4导通,Q1,Q3截至,Y4输出高电平;

③ 当A4输入高电平,B4输入低电平时,Q1,Q3导通,Q2,Q4截至,Y4输出高电平;

④ 当A4输入高电平,B4输入高电平常,Q3,Q4导通,Q1,Q2截至,Y4输出低电平;

2.5 或非门

或非门(NOR gate)是或门和非门的叠加结合。

只有当输入都为低电平(逻辑0)时,输出为高电平(逻辑1),否则输出为低电平(逻辑0)。

逻辑表达式:Y5=(A5+B5)’

表1-5 或非门真值表

图2-5-1 或非门逻辑符号(矩形国标符号与形状特点符号)

图2-5-2 CMOS或非门电路

图2-5-3 CMOS或非门电路工作原理图

如上图所示,CMOS或非门电路的工作原理为:

① 当A5输入低电平,B5输入低电平时,Q1,Q2导通,Q3,Q4截至,Y5输出高电平;

② 当A5输入低电平,B5输入高电平常,Q1,Q4导通,Q2,Q3截至,Y5输出低电平;

③ 当A5输入高电平,B5输入低电平时,Q2,Q3导通,Q1,Q4截至,Y5输出低电平;

④ 当A5输入高电平,B5输入高电平常,Q3,Q4导通,Q1,Q2截至,Y5输出低电平;

2.6 同或门

同或门(XNOR gate)可以只用与非门或则或非门组成,输入相同,输出为高电平(逻辑1),输入相异,输出为低电平(逻辑0)。

逻辑表达式:Y6=A6⊙B6=A6·B6 + A6’·B6’

表1-6 同或门真值表

图2-6-1 同或门逻辑符号(矩形国标符号与形状特点符号)

图2-6-2 同或门实现图

图2-6-3 CMOS同或门电路

图2-6-4 CMOS同或门电路工作原理图

如上图所示,CMOS同或门电路的工作原理为:

①当A6输入低电平,B6输入低电平时,Q1,Q2,Q3,Q4,Q6,Q9导通,Q5,Q7,Q8,Q10,Q11,Q12截至,Y6输出高电平;

②当A6输入低电平,B6输入高电平常,Q3,Q4,Q5,Q7,Q10,Q12导通,Q1,Q2,Q6,Q8,Q9,Q11截至,Y6输出低电平;

③当A6输入高电平,B6输入低电平时,Q1,Q2,Q5,Q8,Q10,Q11导通,Q3,Q4,Q6,Q7,Q9,Q12截至,Y6输出低电平;

④当A6输入高电平,B6输入高电平常,Q5,Q6,Q7,Q8,Q11,Q12导通,Q1,Q2,Q3,Q4,Q9,Q10截至,Y6输出高电平;

2.7 异或门

异或门(XOR gate)由一个与门,或门和与非门组成,输入相异,输出为高电平(逻辑1),输入相同,输出为低电平(逻辑0)。

逻辑表达式:Y7=A7⊕B7=A7·B7’ + A7’·B7

表1-7 异或门真值表

图2-7-1 异或门逻辑符号(矩形国标符号与形状特点符号)

图2-7-2 异或门实现图

图2-7-3 CMOS异或门电路

图2-7-4 CMOS异或门电路工作原理图

如上图所示,CMOS异或门电路的工作原理为:

①当A7输入低电平,B7输入低电平时,Q1,Q2,Q3,Q4,Q8导通,Q5,Q6,Q7,Q9,Q10截至,Y7输出低电平;

②当A7输入低电平,B7输入高电平常,Q3,Q4,Q5,Q6,Q10导通,Q1,Q2,Q7,Q8,Q9截至,Y7输出高电平;

③当A7输入高电平,B7输入低电平时,Q1,Q2,Q5,Q7,Q9导通,Q3,Q4,Q6,Q8,Q10截至,Y7输出高电平;

④当A7输入高电平,B7输入高电平常,Q5,Q6,Q7,Q9,Q10导通,Q1,Q2,Q3,Q4,Q8截至,Y7输出低电平;

三、项目设计

1.原理图设计

首先,打开嘉立创EDA创建新工程,并命名为【数字电路】基本逻辑门分立器件电路,再将原理图文件命名为:SCH_基本逻辑门分立器件电路;

其次,进行元件选型。这里所有元器件都选用贴片元件数字逻辑电路与系统设计第二版答案,元器件都可以在嘉立创EDA的器件库中进行搜索,每一个元元件在立创商城中都有惟一的商品编号,电源插口选用6Pin的TYPE-C母座,使用LED来显示验证各逻辑门的运算关系。

最后,绘制电路原理图,各逻辑门按模块电路界定进行勾画,注明各个电路的作用,添加各逻辑门的符号,真值表和表达式,便于理解学习。

图3-1-1 SCH_电源输入电路

图3-1-2 SCH_PMOS和NMOS电路

图3-1-3 SCH_与门电路

图3-1-4 SCH_或门电路

图3-1-5 SCH_非门电路

图3-1-6 SCH_与非门电路

图3-1-7 SCH_或非门电路

图3-1-8 SCH_同或门电路

图3-1-9 SCH_异或门电路

2.物料清单

3.PCB设计

在完成原理图设计后,经过检测电路与网路联接正确后点击底部菜单栏的 “设计 ”→ “转换原理图到PCB”(快捷键为Alt+I),将PCB文件保存到工程文件中,并命名为:PCB_基本逻辑门分立器件电路。

在勾画边框时,控制在10cm*10cm之内,可以到嘉立创免费打样~

这里的边框为10cm*10cm,添加2mm的圆角。

在进行元件布局时,所有元件放置于顶楼,各逻辑门电路按模块界定摆放,可以通过底部菜单栏中的“设计”→“交叉选择”(快捷键Shift+X)功能快速摆放元器件。在摆放相同元器件时尽量统一方向,方便钎焊。

在进行布线时以底层走线为主,优先走直线,需要转弯的地方以弧形转弯或钝角为主。完成走线检测DRC无误后,添加泪滴和覆铜。

最后,在板上添加丝印标明说明,使电路愈发清晰明了。

图3-2-1 PCB布局布线参考图

顶面勾画完成后,在反面放置丝印标示各逻辑门的符号,真值表和表达式,清晰各个逻辑门的逻辑运算关系,方便理解学习。

图3-2-2 基本逻辑运算丝印赏析图

四、电路调试

1.器件钎焊

第一,先钎焊TYPE-C插口;

第二,PMOS/NMOS;

第三,LED,电阻和电容,最后钎焊开关。

注意钎焊时PMOS和NMOS不要焊错,各逻辑门电路中,上方朝左的为PMOS,下方朝右的是NMOS;LED里面的内阻为1K,其余的均为10K;电容为混频作用,可以不钎焊。

图4-1-1 PCB装配图

在进行点焊时,可在嘉立创EDA的工具栏中点击钎焊辅助工具,实时交互便捷钎焊。

注意钎焊过程中用电安全手不要接触到烙铁头,避免晒伤。

焊接时元器件对准位置,检查机型是否正确。焊接次序应遵守从低到高原则进行,避免影响小元件的点焊。

焊接贴片元器件用钳子捉住时,要等焊锡融化后再移走钳子,否则容易引起漏光。焊接过程注意是否漏光漏焊,避免影响电路性能,导致电路不能正常工作。

图4-1-2 PCB空板-顶面

图4-1-3 PCB空板-底面

图4-1-4 PCBA实物图

2.上电调试

若电工比较粗糙,在点焊完一种元器件,可以目测检测是否漏电,也可用万用表检测。

焊接完成后须要使用万用表检测电源与地是否漏电,焊接过程中有没有出现漏电以及断路的情况,检查无误后方能进行上电测试。

建议采用分步调试,避免其他电路的干扰。

2.1 电源电路

插入TYPE-C通上电后,拨动开关至上方开,电源状态指示灯亮起,电源给整个板子供电,各逻辑门有独立电源开关进行控制。

图4-2-1 电源开关电路

2.2 PMOS电路

拨动打开PMOS电源开关,PMOS电路正常工作。

图4-2-2 PMOS验证工作图

2.3 NMOS电路

拨动打开NMOS电源开关,NMOS电路正常工作。

图4-2-3 NMOS验证工作图

2.4 与门

拨动打开与门电源开关,与门电路正常工作。

图4-2-4 与门验证工作图

2.5或门

拨动打开或门电源开关,或门电路正常工作。

图4-2-5 或门验证工作图

2.6非门

拨动打开非门电源开关,非门电路正常工作。

图4-2-6 非门验证工作图

2.7与非门

拨动打开与非门电源开关,与非门电路正常工作。

图4-2-7 与非门验证工作图

2.8或非门

拨动打开或非门电源开关,或非门电路正常工作。

图4-2-8 或非门验证工作图

2.9同或门

拨动打开同或门电源开关,同或门电路正常工作。

图4-2-9 同或门验证工作图

2.10异或门

拨动打开异或门电源开关,异或门电路正常工作。

图4-2-10 异或门验证工作图

如果你看见了这儿,那么你值得一个点赞!但想要真正把握,还是须要动起手来哦~