1、系统功能

数字电视讯号发生系统的主要任务是形成符合smpte274274m系统标准的18种数字讯号测试图象,ypbpr,rgb两种视频输出插口符合itu-rbt.1120-2/gy/t157-2000演播室高清晰度数字视频讯号插口标准。本系统的核心是图象讯号的编码发生单元fpga,采取单芯片多配置方案可使18种图象讯号便捷地进行配置与加密。由控制,可快速地进行图象切换和格式转换。在普通接入下,系统需生成支持smpte274274m系统标准中的10801080ii6060hz,10801080ii5050hz,10801080pp6060hz、10801080pp5050hz四种标准格式的18种高清晰度电视通用测试图象的数字输出讯号和模拟输出讯号,其标准测试讯号的数码发生内核基于fpga平台实现。在此基础上,本系统提供了一个人工可控功能,即用户可依照按钮,对以上4种标准的18种测试纹样进行切换控制。考虑到输出讯号的实用性,输出的模拟测试讯号和数字测试讯号都必须满足相应的插口标准。为满足以上约束条件,系统功能设计如图1所示。

2、信号形成的原理

数字电视也是彩色电视(只是讯号的表示方式及讯号的处理方式与模拟电视有所不同),因而在考虑数字电视测试讯号发生器包含什么(测试讯号)内容时,本文依照彩色电视的基本特征,首先应考虑包含通常彩色电视广播测试图的基本内容,比如观察显示设备扫描非线性失真和几何失真的棋盘讯号和圆讯号,观察图象清晰度和帧率的多波群或扫频讯号,观察色温非线性失真情况以及显示器色温调整是否正确的灰度级(或阶梯波)讯号,观察彩色再现是否正确的彩条讯号等;另外还考虑降低了在视频检测中最常用的2t脉冲讯号、彩色多波群讯号和彩色阶梯波讯号,以及更为直观的斜波讯号等,便于全面地观察和评价彩色电视系统或设备的基本质量。

数字电视讯号发生器的fpga设计

1、fpga设计原理

fpga是整个数字电视测试讯号发生器系统的核心,各类测试讯号编码都在这一部份实现。fpga设计原理如图2所示。

所有测试讯号的编码均基于图象的行/列座标而形成数字电视回看功能,其行座标和列座标分别为象素计数器和行计数器按照全局时钟上升沿进行计数所得数值。行域讯号生成模块对行计数器输出的值进行阀值界定,将测试图象按行界定为不同的区域,称为行域。在不同的行域中,按照象素计数器值进行不同的象素区域界定,将测试图象进一步界定为相对独立的讯号编码区域,每位区域对应一个标志讯号。此时,行/列座标与讯号编码区域一一对应,称当前输出讯号所在行/列所对应的讯号编码区域为当前域,其标志讯号为当前域标志讯号。最后,按照当前域标志讯号对测试讯号的定时基准码、有效区域等讯号进行编码,由测试纹样编码模块输出全图像讯号数字视频份量的码值。

2、fpga设计总体结构

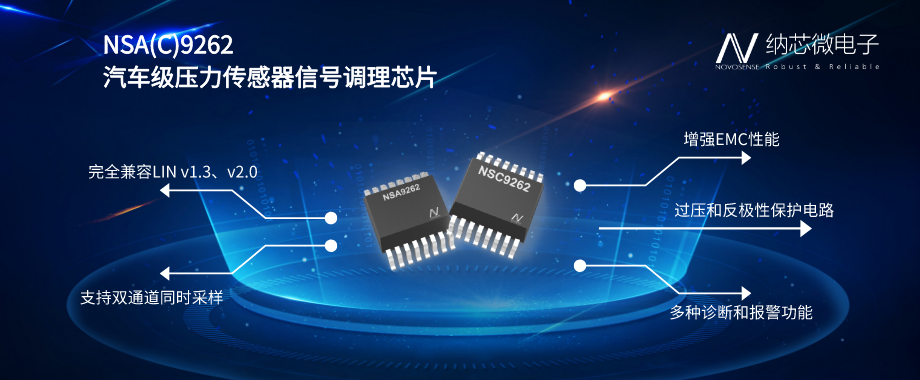

该模块是系统工作的核心,如图3所示,单芯片多配置方法中的主芯片,可提供支持smpte274274mm108010801080ii6060hz/10801080ii5050hz格式的18种高清电视通用测试图,如综合测试卡讯号、smpte219-2002测试图、smpte198-1998场检查图等。主芯片按照控制模块输出的纹样/格式选择讯号,选择不同的配置程序,输出相应测试图的数字y、cb/cr信号码值,以及相关的同步/消隐控制讯号。

2.2.2图象讯号配置与加密单元

该模块由8片配置芯片xcf0202s与1片xc95144xl组成,是成功实现单芯片多配置方案的关键模块。配置程序选择联接开关即按照控制模块输出的5b配置芯片选择讯号,选择相应测试纹样的配置芯片prom的系统可编程jtag连线与主芯片对应引脚相联接。

2.2.3图象讯号输出单元

数字输出部份由驱动电路与插口芯片组成,模拟输出部份由ti公司的d/a转换芯片ths8200及其内部ifir数字混频器以及外围运算放大器电路实现数模转换功能。可按照控制模块的纹样/格式以及模拟输出插口类型选择讯号,将y、cb/cr的并行数字视频份量讯号转换为模拟输出,或则转换为rgc模拟输出。

2.2.4人机界面与控制单元

控制模拟讯号输出类型,并通过输出i2c总线对d/a转换芯片的寄存器进行相应配置。按照外部输入讯号,形成相应的纹样/格式选择讯号和配置芯片选择讯号,控制主芯片与配置芯片的断电与上电时序,与选择联接开关模块共同完成测试图切换功能。这些单片多配置方案,讯号转换速率很快,与单片单配置方案一样,为微秒级。

2.3fpga测试图象讯号形成

综合测试图象讯号实际上是由多种测试讯号合成的,包括圆讯号、棋盘讯号、多波群讯号、彩条讯号等。设计将综合测试图分为三个层次实现。第一层设计采用圆讯号作为选通讯号,圆讯号外的视频有效区域输出棋盘讯号,而圆讯号内的视频有效区域输出多种测试讯号;第二层设计采用行计数器值作为讯号界定边界值,不同的行域输出不同的测试讯号数字电视回看功能,用于测试设备的各类性能;第三层设计采用象素计数器值作为讯号内部的区域界定参数,完成每种测试讯号的生成。其代码设计基本框图如图4所示。

其中圆外的棋盘讯号采用灰底白格棋盘,圆内讯号从上至下依次设计为白场、信号、2t脉冲讯号、黑白场交织讯号、100%彩条讯号、亮度多波群讯号、6电平色温五阶梯讯号、2t脉冲讯号与色亮信噪比差观察讯号。其中黑白场交织讯号中黑场与白场交替出现,每场宽80个象素点;彩条讯号电平符合100/0/100/0,每位彩条讯号宽160个象素点;色温多波群讯号每波带讯号宽160个象素点;6电平色温五阶梯讯号每阶梯宽160个象素点;2t脉冲讯号为半幅值长度为34ns、幅度为80%视频幅度的2t余弦平方正脉冲和负脉冲讯号;按照黄、红色色温电平相差较大及易于观察等诱因,色亮信噪比差观察讯号采用黄、红讯号,其红黄交界处与其前面的2t脉冲峰值点在测试图中的水平方向位置相一致。为有效借助fpga资源,并减短开发周期,综合测试图中的多波群讯号直接调用rom的ip核实现。