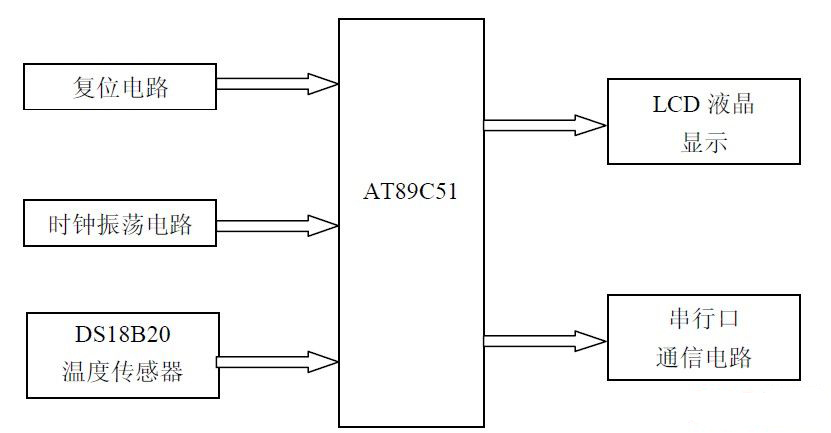

现场可编程门阵列PGA是近些年来发展迅速的大规模可编程逻辑元件,它具有设计周期短,片内资源丰富,可无限次加载和现场可编程等特性。在FPA上实现模糊控制器是一种介于专用集成电路(SIC)和通用处理器之间的方案,具有电子产品的高速率、高可靠性、小型化、集成化、低帧率、保密性能好、具有自主知识产权、产品上市快等优势。模糊控制器不须要控制对象的精确物理模型,是一种基于规则的控制,根据操作人员的控制经验和专家的知识,通过查表得到控制量。因而,模糊控制器具有响应快,超调量小,鲁棒性强等特性。它才能克服系统中模型参数变化和非线性等不确定诱因,在大滞后、非线性系统中得到广泛应用。随着DA技术的发展,FPA在数字逻辑系统中发挥越来越重要的作用,采用硬件描述语言的硬件电路设计方式得到了广泛应用。本文借助HDL硬件描述语言在G芯片上设计一种简化的模糊控制器。一模糊控制器的结构及其PGA实现流程输出数据库规则库模糊化插口推理机解模糊插口图1模糊控制器的组成框图给定值模糊量化处理模糊控制规则模糊决策非模糊化处理传感被控对象执行机构ked/dtkcku图2模糊控制器机布光因为一维模糊控制器的动态性能不能令人满意,三维及三维以上的模糊控制器结构复杂,构建模糊控制规则比较困难,因而通常采用双输入单输出的二维模糊控制器。

典型的两输人单输出模糊控制器的结构如图2所示,它由知识库、模糊化、模糊推理和逆模糊化4部份构成。知识库向模糊化模块提供模糊量的隶属函数形态,使模糊化模块在接收到外部的精确量输人以后,才能将其转换成相对应时模糊量及隶属度。同时,知识库向模糊推理模块提供控制规则,由模糊推理模块执行推理过程,由输人的模糊量推出输出的模糊量。知识库也向反模糊化模块提供模糊量的隶属函数形态,反模糊化插口则将输出的模糊量及隶属度转换成与之对应的精确量。论域和模糊状态应依照问题的实际情况而定,现今假定e,ec和的模糊子集均为NB,NM,S,Z,PS,PM,PB,模糊论域均为-4,-3,2,-,0,1,2,3,设e的基本论域为2,2,ec的基本论域为-1,1,u的基本论域为-5,。则ke=2,kc=4,k=1。25。模糊控制器的FPG设计流程如图3所示模糊控制器功能定义模糊控制器算法设计确定总体结构界定功能模块对个功能模块进行vhdl语言描述综合,仿真Fpga配置下载硬件测试图3模糊控制器的fpga实现流程图模糊化模块.隶属函数的选定模糊化过程须要用到隶属函数,隶属函数是模糊控制中的关键问题。隶属函数大多依赖经验或处理便捷而选定。

选定时起码要遵守条原则:表示隶属函数的模糊集合必须是凸模糊集合;变量所取隶属函数是对称和平衡的;隶属函数要遵照语意次序和防止不恰当的重叠。因而,此文确定的E和C的隶属函数形状如图4所示图E和C的隶属函数形状2隶属函数的储存将上述隶属函数存在2个RAM表中,则在模糊化处理时可进行并行处理,处理便捷,且速率提升一倍。表示方式如图所示。图隶属函数的储存形式在图4中,三角形是等边三角形,矩形的下底是上底的2倍。可见由斜边长度和斜边中点就可以确定隶属函数的所有信息。分别用一个字节表示每位语言变量的斜边长度(实际长度的一半),用个位(bi)表示斜边中点位置。这样,全部信息只须要8个字节,以及8个3位就可以表示了:斜边长度表示为:with0模糊集合的表示方法,widthl,,wit7斜边中点表示为:cener0,cente,center7这部份信息存于一个偶数表和一个质数表中,分别表示标号为质数和奇数的斜边长度和斜边中点信息。3.隶属度的估算模糊化模块的功能主要包括2部份:把输人的精确量进行尺度变换,变换到相应的论域范围;将己变换到论域范围的输入量进行模糊化处理,主要是估算各个输人量的隶属度。为了简化处理,将输人值进行均匀量化。

因为A/D转换器取样后输人的值为8位,其范围是0一255,均匀量化后各个论域表示见表1。这样模糊化模块的主要工作就是估算输人值的隶属度,如图所示。表1论域f化和表示方式图隶属度图据图6,输人变量为时,其隶属度为为实现上述估算,须要用到一个加法器,一个减法器和一个除法器。由隶属度的性质可知,估算的结果肯定是小数。为了实现便捷,可将分子的估算结果左移位,使分子弄成6位,而分母是位,因而,估算结果是位。加法器和减法器的实现比较容易,重点放到6位乘以8位的除法器的实现上。除法器采用普通的乘法运算,并配合移位一加法形式来实现,可节约硬件制做成本。加法运算的算法流程如图7所示,图中:为被除数;b为除数;q为商;r为余数;s为控制加法运算开始执行的控制讯号;dn表示运算完成;c为加法计数器的计数值。图加法运算的算法流程图据上述算法编撰HDL程序,可实现除法器运算。除法器是模糊化模块的关键部件,完成了除法器的设计,也就基本上完成了模糊化模块的数据处理模糊推理模块模糊控制器的核心是模糊推理,模糊推理的基础是模糊控制规则。模糊控制规则是用语言表示的模糊条件句子,储存在模糊控制器的知识库中,可以通过插口由控制专家输人或更改。

两输人单输出的模糊控制规则方式为模糊推理常采用amdni推理,亦称为Ma-Mi推理。设两输人单输出模糊控制器的输人量是ISANS,则依照模糊控制规则进行推理,可以得出输出模糊控制量:(用模糊集合C表示):式中包括了3种主要的模糊逻辑运算:and运算,一般采用求交(取小)的方式;蕴涵运算“”采用求交法;合成运算“。”,采用Max-Mi技巧。假定有如下条模糊控制规则则Maani推理的机理如图7所示。图中,1模糊集合的表示方法,2:通过最小化运算求出,最左边的模糊量图形通过最大化运算求出,C就是最终的推理结果。可见,模糊推理主要包括最小化运算模块和最大化运算模块。图8Manni推理的机理此处知识库中的模糊控制规则,每一条可用一个字节来储存,具体储存格式为:000000X000001XX0010X00011XX111100XX1111XX这样就可以把输人的语言值作为规则表的地址进行查找。由隶属函数的特性可知,对于每位输人变量,最多可以并行输出个语言值和个隶属度。对于两输人系统,最多输出4个语言值和4个隶属度。这样,对于一个两输人系统,最多激活条模糊规则,即这样,最终模糊量C的推理过程与只有2条规则时完全类似,只须要最小化运算和最大化运算。

实现最小化运算的关键是设计出一个最小比较器。因为每位前件最多激活2条模糊规则,所以设x1和x2是第1个前件的隶属度,y1和y2是第2个前件的隶属度,,1和c2分别是对应于条模糊控制规则的输出量的隶属度。比较器的行为可以描述如下最小化运算的结果,c1和c4再输人到最大化模块中,用于完成模糊规则合并的过程。最大化模块与最小化模块的实现方式类似。逆模糊化模块反模糊化一般采用加权平均法,对于论域为离散的情况有因为隶属函数采用位二补码表示,而所涉及的模糊规则最多为4条,所以分子运算须要个位x位的乘法器,3个10位加法器,分母须要3个位加法器。据悉,还须要一个12位10位的除法器。除法器的设计方式与模糊化模块中的设计方式相同。而乘法器的设计方式有多种,可以借助工具软件自带的参数可设置兆功能块LM一ultipir进行订制。由上所述,反模糊化模块须要乘法器和除法器,因而它是最浪费芯片资源,也是最历时的一个模块。设计模糊控制器按照模糊控制器的特性及上述描述原理,采用模块化设计方式,本文将模糊控制模块分为四块分别进行设计,如图所示。clk为全局时钟,g和f为输入给定和反馈,u为输出控制量,设g,f,和u的位数为八位。

模糊控制模块内部构架分为四个模糊:减法器模块,离散化模块,建表模块和处理模块。用VDL硬件描述语言在ale公司的rti50进行描述,产生四个模块并进行综合,见图所示。图9模糊控制器各个模块的作用分别如下描述:减法器模块(iafqi)主要是借助给定值g和反馈值f估算偏差和偏差变化率c。进行加法运算时,总是数值大的除以数值小的,正负号分别由eo和co标示,不须要考虑溢出和借位等问题。离散化模块(sanua)的作用时把减法器模块得到的偏差e和偏差变化率ec在各自的论域范围内进行离散处理。离散时把量化因子ke和c乘入。建表模块(jinbiao)的作用是把控制总表用vhdl语言的方式描述,此控制表是模糊控制表乘上比列因子u后的实际值。因为控制表中的数是当前控制变化量,还不能直接作用于被控对象,处理模块的作用是按照当前控制变化量,在前一次控制量的基础上进行运算得到这次控制量。同时规定控制量的上下限,上限依照具体情况而定,下限是零。仿真仿真波形如右图,从仿真图可以看出,在给定值不变的情况下,控制量随着反馈值f的变化而变化,变化规律与理论上的模糊控制系统的输出规律基本一致.图0仿真波形图结束语本文采用VHDL硬件描述语言在alra公司的urtii5实现了模糊控制器,而且进行了仿真,仿真发觉该模糊控制器基本符合模糊控制器的性能要求。

附录:模糊控制器各个模块hdl语言描述:减法器模块的vhdl语言的程序如下:BRAIEEE;SEEE。ST_LOGIC114。AL;SEEEE。STDLOGCARITH。ALL;eNTITYhuISpORT(g:INSD_LOGIC_CTO(7DWNTO0);f:INSTD_I_VCOR(7DNTO);ck:INSDLOGIC;e:OUSTD_LOGC_VCTOR(7DOO0);e:OTST_OGI_VECTO(7DOWN);eo:OUTSDLOIC;co:USTDLOGC);eNm;HIEURErtOFmhuSSINAa,b:TDLGC_VCTR(7DNT0);ignlm,n:SD_LOGIC;eginprces(lk)bginifclenandcl=1thnffgthna=f-g;m=1;lsiffgtheag-f;m=0;endif;b;bthnec=b-a;c=0;elsifteec=b-a;co=1;esifm0ann1hec=+;co